Study with the several resources on Docsity

Earn points by helping other students or get them with a premium plan

Prepare for your exams

Study with the several resources on Docsity

Earn points to download

Earn points by helping other students or get them with a premium plan

Community

Ask the community for help and clear up your study doubts

Discover the best universities in your country according to Docsity users

Free resources

Download our free guides on studying techniques, anxiety management strategies, and thesis advice from Docsity tutors

The final exam questions for a computer science and electrical engineering (cs/ee) 577 course focused on networking. The exam covers topics such as virtual path/circuit tables, routing memory requirements for single-stage switches, queue control, and network conditions for non-blocking traffic. Students are expected to solve problems related to determining output values for virtual path/circuit tables, calculating required entries and bits per entry for input and output tables, handling cells in a queue, estimating blocking probability using lee’s method, and identifying connections in virtual circuit tables.

Typology: Exams

1 / 10

This page cannot be seen from the preview

Don't miss anything!

This is a closed book exam.

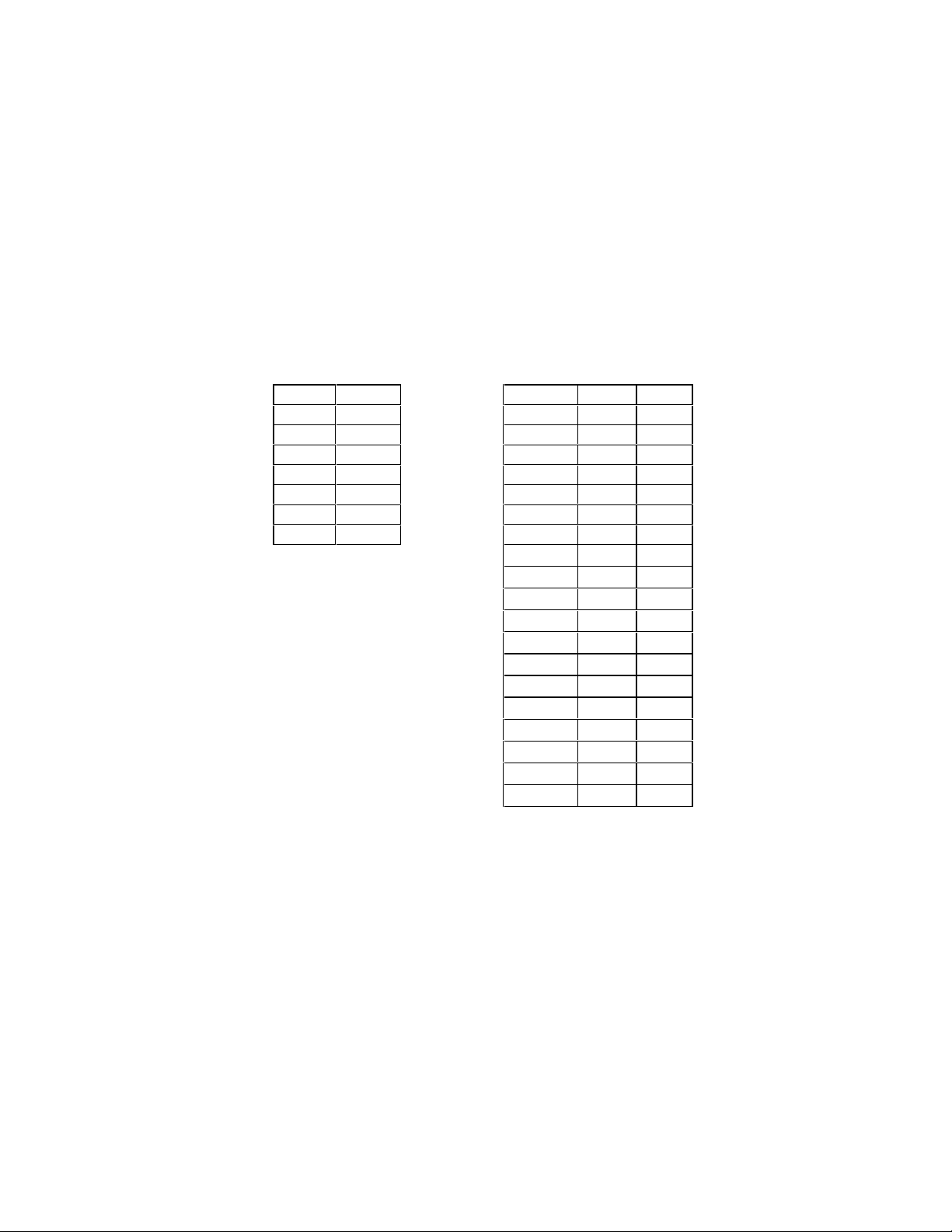

base size output VPI VCI (^0 0 5 0 5 22 ) (^1 5 3 1 2 15 ) (^2 0 5 2 3 32 ) (^3 8 6 3 4 11 ) (^4 14 4 4 1 13 ) 5 18 2 5 3 31 5 (^6 0 5 6 5 24 ) (^7 0 5 7 7 16 ) (^8 2 24 ) (^9 4 31 ) (^10 8 22 ) (^11 11 54 ) (^12 15 11 ) (^13 7 18 ) (^14 12 12 ) (^15 11 13 ) (^16 13 15 ) (^17 15 22 ) (^18 12 21 ) 19 0 12 35

When a cell with (VPI,VCI)=(3,5) arrives at the input port with this VPI/VCI table, what output is the cell sent to? What are the values of the (VPI,VCI) field of the forwarded copy?

Repeat for (2,2), (5,1) and (6,3).

Consider a single-stage switch with 16 ports and using a bus to interconnect the ports. Each input has a virtual circuit table that for point-to-point virtual circuits specifies the output port and output VCI a cell with a given input VCI is to be sent to; for multipoint virtual circuits, it instead specifies a Broadcast Channel Number. The BCN is used at the output ports for another table lookup that yields the outgoing VCI. Assume that we want to support a total of 4096 entries on each input link and each output link and we want to allow up to 500 VCIs on each output to be associated with multicast virtual circuits. How many entries must each of the input tables have and how many bits per entry?

How many entries must each of the output tables have and how many bits per entry, assuming that the output tables are implemented using direct lookup?

How many entries must each of the output tables have and how many bits per entry, assuming that the output tables are implemented using CAMs?

Assuming the queue controller does not implement early packet discard, or any similar method of preserving packet integrity, approximately what fraction of the packets sent are corrupted (that is, have at least one of their cells lost)?

Suppose the queue controller does implement early packet discard and that the buffer is large enough to ensure that it never overflows and never becomes empty during the overload period. What fraction of the packets are lost in this case?

Approximately what fraction of the time is the buffer below the threshold?

Suppose we were to add another virtual circuit sending 4 Kbyte packets at 1 Mb/s. Approximately what fraction of packets sent by this new virtual circuit will be lost?

What condition must be satisfied in order for Cn,d,r to be strictly nonblocking for multipoint traffic, assuming b =0.

What condition must be satisfied in order for Cn,d,r to be reroutably nonblocking for multipoint traffic, assuming b =0 and a first stage fanout restriction of f.

What condition must be satisfied in order for Bn,d to be strictly nonblocking for point-to-point traffic, assuming b =0.

What condition must be satisfied in order for Bn,d ; Bn,d to be reroutably nonblocking for multipoint traffic, assuming b =0.

Which of these has the best cost/performance in large configurations?

Which has the worst?

Give two reasons that account for the superiority of the best over the worst.

If the copy network is replaced with one having 16 outputs and the copy range calculation is changed appropriately, how many cells will pass through to the copy network outputs?

strictly nonblocking

rearrangeably nonblocking

reroutably nonblocking

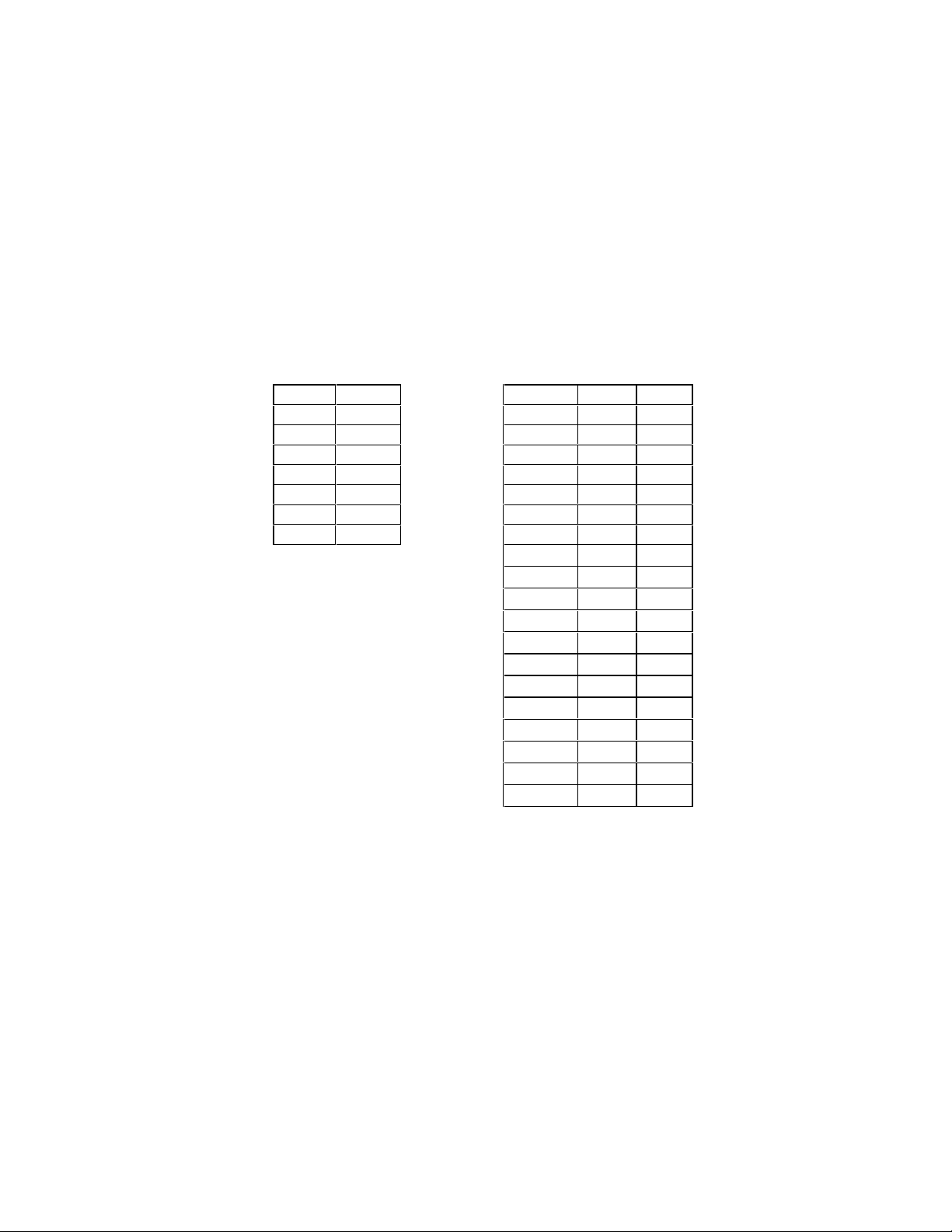

VCI 0 1 2 3 4 5 6 7 8 9 input 0 (3,3),(7,0) 1 (5,1) 2 (5,2)^ (3,2),(4,0)^ (1,4),(2,8)^ (5,1) 3 (1,7),(2,0) 4 (7,7),(5,9)^ (6,2) 5 (2,6),(6,1) 6 (6,7),(7,2)^ (5,1) 7 (5,9),(7,1)^ (5,1)