Study with the several resources on Docsity

Earn points by helping other students or get them with a premium plan

Prepare for your exams

Study with the several resources on Docsity

Earn points to download

Earn points by helping other students or get them with a premium plan

Community

Ask the community for help and clear up your study doubts

Discover the best universities in your country according to Docsity users

Free resources

Download our free guides on studying techniques, anxiety management strategies, and thesis advice from Docsity tutors

Material Type: Lab; Class: Senior Project; Subject: Electrical & Computer Engineer; University: Lafayette College; Term: Fall 2007;

Typology: Lab Reports

1 / 2

This page cannot be seen from the preview

Don't miss anything!

Laboratory 4 – RS-232 Serial Data Transmission September 21, 2007

Goals

Requirements

You will develop an FPGA-based Asynchronous Serial Transmitter that meets the following requirements:

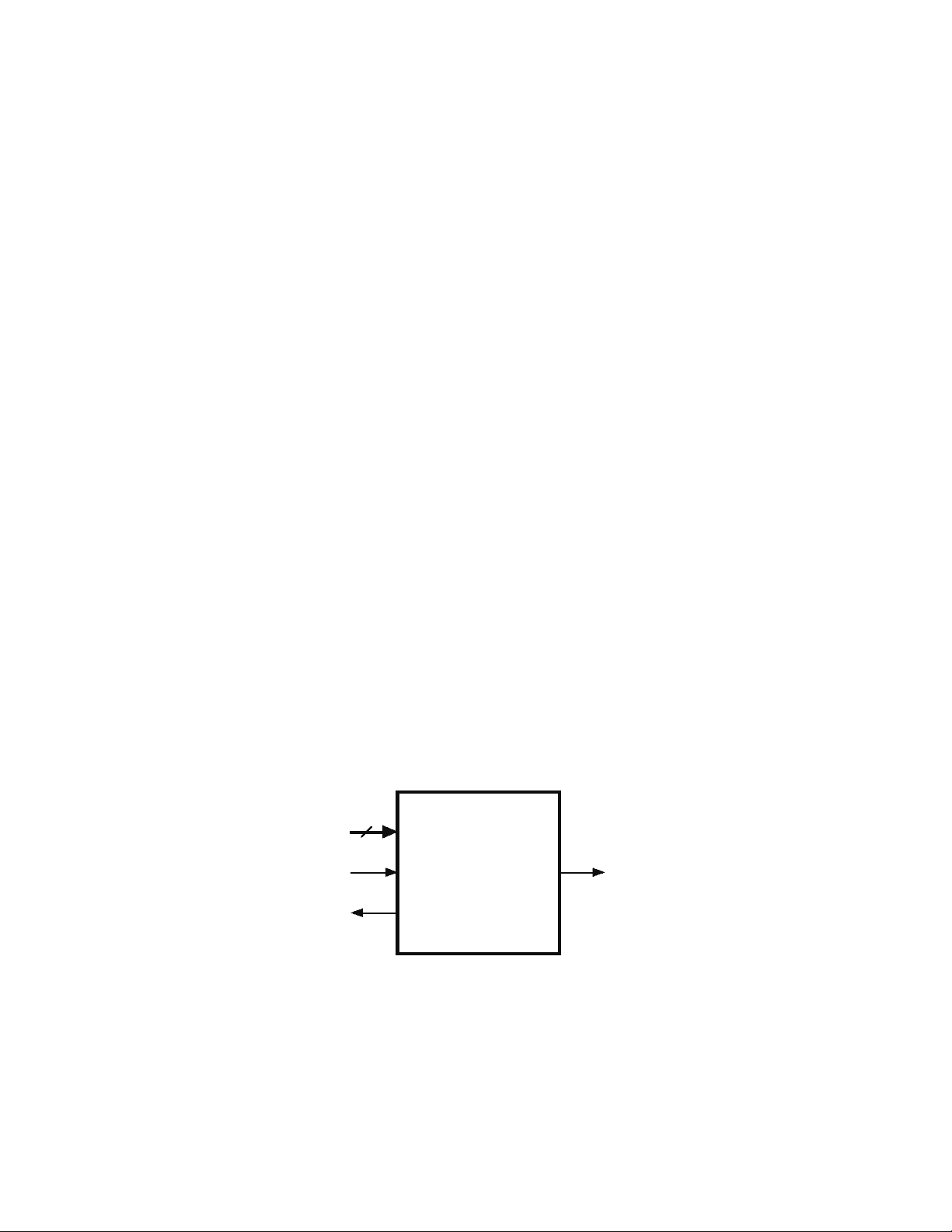

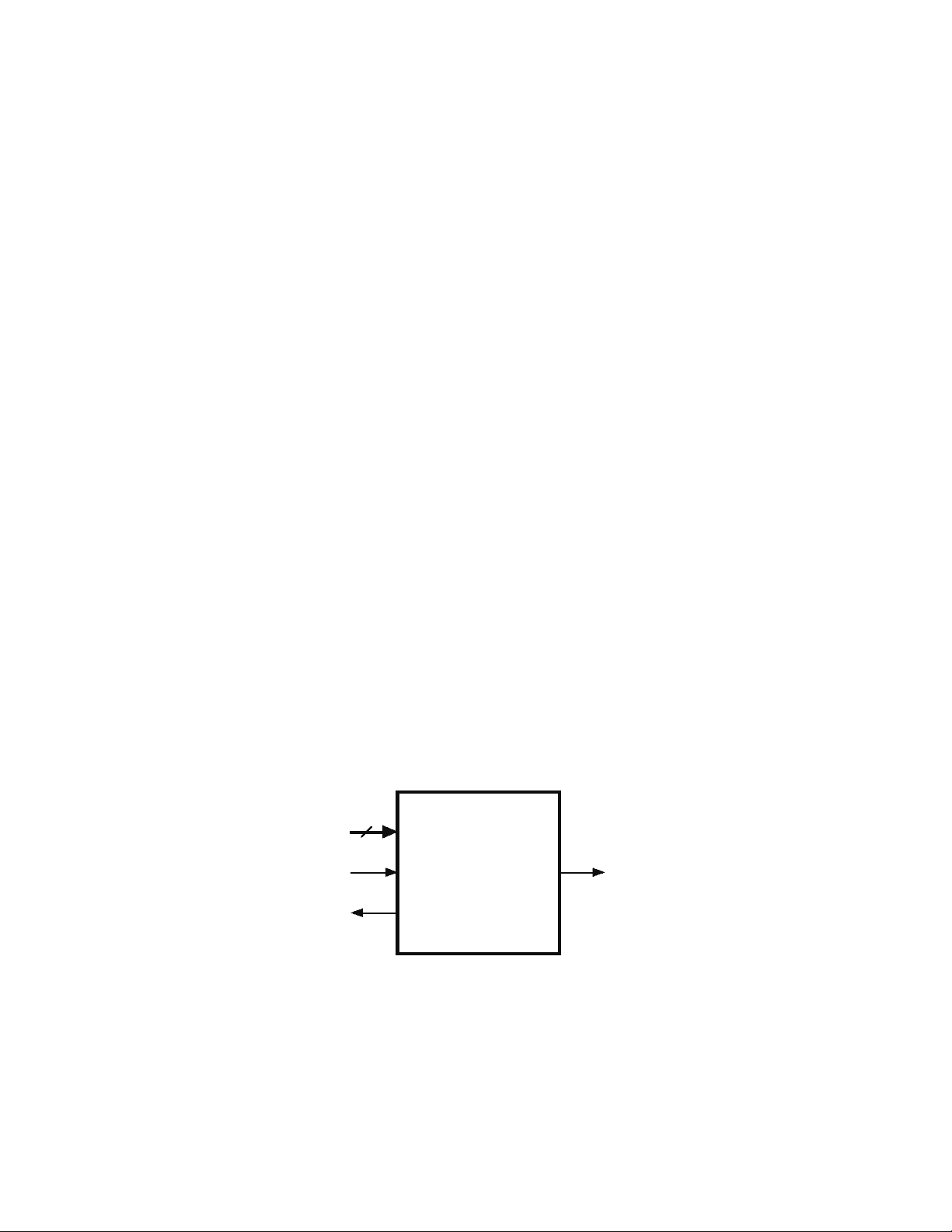

DATA

START

RDY

TxD

Transmitter 8

Deliverables

Background

Asynchronous serial data transmission protocols such as RS-232 involve sending data serially at a known transmission rate called the baud rate. The RS-232 protocol is used to transmit data between computers and terminals. Data is transmitted in the following form:

8 Data Bits

LSB MSB

START BIT

STOP BIT T = 1/(Baud Rate)

T

DATA SIGNAL

When no characters are being transmitted, the DATA signal remains high. When a character is transmitted, it is sent one bit at a time at the baud rate but is preceded by a start bit that is always asserted low. In addition, the data bits are followed by a stop bit that is always asserted high. After the complete transmission of a character and its start and stop bits, additional characters may be sent immediately if desired following the same protocol. If an additional character is not sent immediately after the stop bit, the data signal remains high until a new character is sent an indefinite time later. The protocol is asynchronous because the transmitter sending the data and the receiver that receives the data operate using different clocks (they may be separated by a large distance, so distributing the clock is impractical).

An asynchronous serial transmitter is simple to implement using a 10-bit shift register and a little extra hardware. When a character is ready to be transmitted, it is loaded in parallel into the shift register along with start and stop bits. Data is then shifted out at the baud rate until the shift register has a value of zero (since the stop bit is always 1, the shift register will not be zero until the stop bit is shifted out of the shift register).

The Spartan 3 Starter Kit board includes an RS-232 interface that can be connected to a cable to a PC running HyperTerminal for testing. The RS-232 ports are defined in the top-level “s3board.v” file as input port “ rxd_in ” and output port “ txd_out ”. Use the “txd_out” port to test your Transmitter Design.